# Z80 CPU 2nd EDITION ISSUED MAY 1982

# **CONTENTS**

| ASSEMBLY<br>MNEMONIC | OPERATION                                                      | page     |

|----------------------|----------------------------------------------------------------|----------|

| ADC HL, ss           | Add with Carry Reg. pair ss to HL                              | 3        |

| ADC A, s             | Add with carry operand s to Acc                                | 4        |

| ADD A, n             | Add value n to Acc                                             | 6        |

| ADD A, r             | Add Reg. r to Acc                                              | 7        |

| ADD A, (HL)          | Add location (HL) to Acc                                       | 8        |

| ADD A, $(IX + d)$    | Add location (IX+d) to Acc.                                    | 9        |

| ADD A, $(IY + d)$    | Add location (IY + d) to Acc.                                  | 10       |

| ADD HL, ss           | Add Reg. pair ss to HL                                         | 11       |

| ADD IX, pp           | Add Reg. pair pp to IX                                         | 12       |

| ADD IY, rr           | Add Reg. pair rr to IY                                         | 13       |

| AND s                | Logical 'AND' of operand s and Acc.                            | 14       |

| BIT b, (HL)          | Test BIT b of location (HL)                                    | 16       |

|                      | Test BIT b of location (IIX)                                   | 17       |

| BIT b, $(IX + d)$    | Test BIT b of location (IX+d)                                  | 19       |

| BIT b, $(IY + d)$    |                                                                | 21       |

| BIT b, r             | Test BIT b of Reg. r                                           | 22       |

| CALL cc, nn          | Call subroutine at location nn if condition cc is true         |          |

| CALL nn              | Unconditional call subroutine at location nn                   | 24       |

| CCF                  | Complement carry flag                                          | 26       |

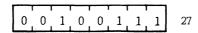

| CP s                 | Compare operand s with Acc.                                    | 27       |

| CPD                  | Compare location (HL) and Acc. decrement HL and BC             | 29       |

| CPDR                 | Compare location (HL) and Acc. decrement HL and BC, repeat     | -        |

| CPI                  | until BC = 0                                                   | 30       |

| CPI                  |                                                                | 32       |

| ODID                 | BC                                                             | 32       |

| CPIR                 | Compare location (HL) and Acc. increment HL, decrement BC      | 33       |

| an.                  | repeat until BC = 0                                            |          |

| CPL                  | Complement Acc. (l's comp.)                                    | 35       |

| DAA                  | Decimal adjust Acc.                                            | 36       |

| DEC m                | Decrement operand m                                            | 38       |

| DEC IX               | Decrement IX                                                   | 40       |

| DEC IY               | Decrement IY                                                   | 41       |

| DEC ss               | Decrement Reg. pair ss                                         | 42       |

| DI                   | Disable interrupts                                             | 43       |

| DJNZ e               | Decrement B and Jump relative if $B = 0 \dots$                 | 44       |

| EI                   | Enable interrupts                                              | 46       |

| EX (SP), HL          | Exchange the location (SP) and HL                              | 47       |

| EX (SP), IX          | Exchange the location (SP) and IX                              | 48       |

| EX (SP), IY          | Exchange the location (SP) and IY                              | 49       |

| EX AF, AF'           | Exchange the contents of AF and AF'                            | 50       |

| EX DE, HL            | Exchange the contents of DE and HL                             | 51       |

| EXX                  | Exchange the contents of BC, DE, HL with contents of BC', DE', |          |

|                      | HL' respectively                                               | 52       |

| HALT                 | HALT (wait for interrupt or reset)                             | 53       |

| IM 0                 |                                                                | 54<br>54 |

|                      | Set interrupt mode 0                                           | 55       |

| IM 1                 | Set interrupt mode 2                                           | 55<br>56 |

|                      |                                                                |          |

| IN A, (n) IN r, (C) INC (HL) INC IX INC (IX+d) INC IY INC IY INC (IY+d) INC r INC ss | Load the Acc. with input from device n                                                                                                                                        | 3<br>0<br>1<br>2<br>3 |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| IND                                                                                  | Load location (HL) with input from port (C), decrement HL and B                                                                                                               | 3                     |

| INDR                                                                                 | Load location (HL) with input from port (C), decrement HL and decrement B, repeat until B=0                                                                                   | ,                     |

| INI                                                                                  | Load location (HL) with input from port (C); or increment HL                                                                                                                  |                       |

| nun.                                                                                 | and decrement B                                                                                                                                                               | }                     |

| INIR                                                                                 | Load location (HL) with input from port (C), increment HL and decrement B, repeat until B=0                                                                                   | ,                     |

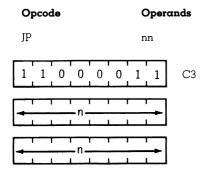

| JP (HL) JP (IX) JP (IY) JP cc, nn JP nn                                              | Unconditional Jump to (HL) 72 Unconditional Jump to (IX) 73 Unconditional Jump to (IY) 74 Jump to location nn if condition cc is true 75 Unconditional Jump to location nn 76 | 3                     |

| JR C, e                                                                              | Jump relative to PC + e if carry = 1                                                                                                                                          |                       |

| JR e                                                                                 | Unconditional Jump relative to PC+e                                                                                                                                           |                       |

| JR NC, e<br>JR NZ, e                                                                 | Jump relative to PC + e if carry = 0                                                                                                                                          |                       |

| JR Z, e                                                                              | Jump relative to PC+e if zero $(Z=1)$                                                                                                                                         |                       |

| LD A, (BC)                                                                           | Load Acc. with location (BC)                                                                                                                                                  |                       |

| LD A, (DE)                                                                           | Load Acc. with location (DE)                                                                                                                                                  | 3                     |

| LD A, I                                                                              | Load Acc. with I                                                                                                                                                              |                       |

| LD A, (nn)<br>LD A, R                                                                | Load Acc. with location nn                                                                                                                                                    |                       |

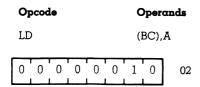

| LD (BC), A                                                                           | Load Acc. with Reg. R                                                                                                                                                         |                       |

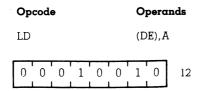

| LD (DE), A                                                                           | Load location (DE) with Acc.                                                                                                                                                  |                       |

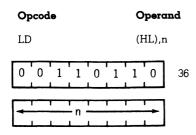

| LD (HL), n                                                                           | Load location (HL) with value n                                                                                                                                               |                       |

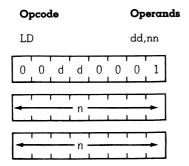

| LD dd, nn                                                                            | Load Reg. pair dd with value nn 90                                                                                                                                            | )                     |

| LD dd, (nn)                                                                          | Load Reg. pair dd with location (nn) 91                                                                                                                                       |                       |

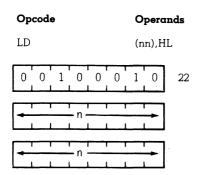

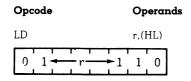

| LD HL, (nn)<br>LD (HL), r                                                            | Load HL with location (nn) 92  Load location (HL) with Reg. r 93                                                                                                              |                       |

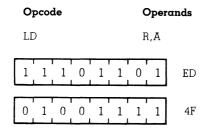

| LD (IIL), I<br>LD I, A                                                               | Load I with Acc. 94                                                                                                                                                           |                       |

| LD IX, nn                                                                            | Load IX with value nn                                                                                                                                                         |                       |

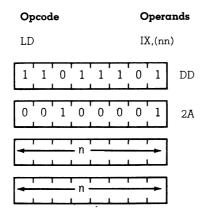

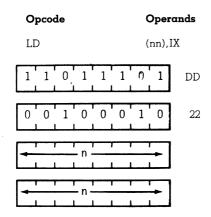

| LD IX, (nn)                                                                          | Load IX with location (nn)                                                                                                                                                    |                       |

| LD (IX + d), n                                                                       | Load location (IX + d) with value n                                                                                                                                           |                       |

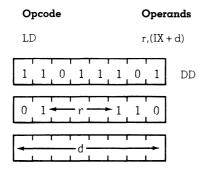

| LD (IX+d), r<br>LD IY, nn                                                            | Load ly with value and ly with Reg. r                                                                                                                                         |                       |

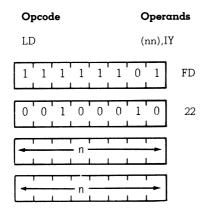

| LD II, nn<br>LD IY, (nn)                                                             | Load IY with value nn 99 Load IY with location (nn) 100                                                                                                                       |                       |

| LD (IY + d), n                                                                       | Load IY with location (nn) 100  Load location (IY + d) with value n 101                                                                                                       |                       |

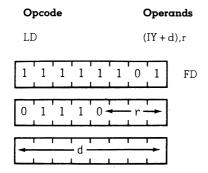

| LD (IY + d), r                                                                       | Load location (IY + d) with Reg. r                                                                                                                                            |                       |

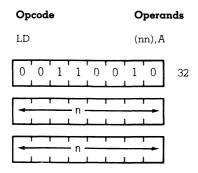

| LD (nn), A                                                                           | Load location (nn) with Acc                                                                                                                                                   |                       |

|                                                                                      |                                                                                                                                                                               |                       |

| LD (nn), dd LD (nn), HL LD (nn), IX LD (nn), IY LD R, A LD r, (HL) LD r, (IX+d) LD r, (IY+d) LD r, r LD r, r LD SP, HL LD SP, IX LD SP, IY LDD | Load location (nn) with Reg. pair dd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDDR                                                                                                                                           | Load location (DE) with location (HL), decrement DE, HL and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LDI                                                                                                                                            | BC; repeat until BC = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LDIR                                                                                                                                           | Load location (DE) with location (HL), increment DE, HL, decre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

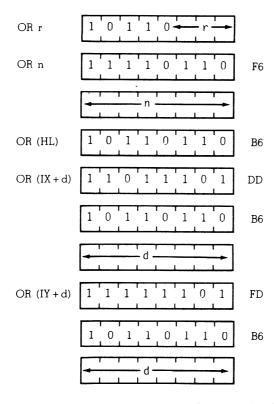

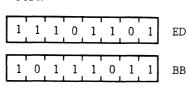

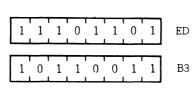

| NEG<br>NOP<br>OR s<br>OTDR                                                                                                                     | Negate Acc. (2's complement) 123 No operation 124 Logical 'OR' of operand s and Acc. 125 Load output port (C) with location (HL) decrement HL and B, repeat until B = 0 127 Load output port (C) with location (HL), increment HL, decrement B, repeat until B = 0 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

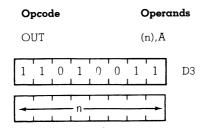

| OUT (C), r<br>OUT (n), A<br>OUTD<br>OUTI                                                                                                       | Load output port (C) with Reg. r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

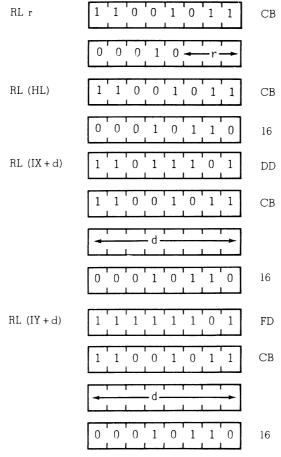

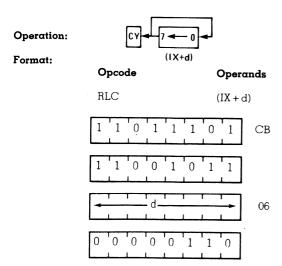

| POP IX POP IY POP qq PUSH IX PUSH IY PUSH qq RES b, m RET RET cc RETI RETN RL m RLA RLC (HL) RLC (IX+d) RLC (IY+d)                             | crement B         134           Load IX with top of stack         135           Load IY with top of stack         136           Load Reg. pair qq with top of stack         137           Load IX onto stack         138           Load IY onto stack         139           Load Reg. pair qq onto stack         140           Reset Bit b of operand m         141           Return from subroutine         143           Return from subroutine if condition cc is true         144           Return from interrupt         146           Return from non maskable interrupt         147           Rotate left through carry operand m         148           Rotate left Acc. through carry         150           Rotate location (HL) left circular         151           Rotate location (IX + d) left circular         153           Rotate location (IY + d) left circular         155 |

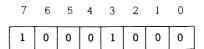

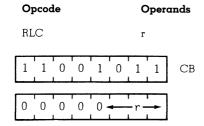

| RLC r             | Rotate Reg. r left circular                                | 157 |

|-------------------|------------------------------------------------------------|-----|

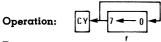

| RLCA              | Rotate left circular Acc                                   | 159 |

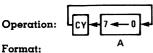

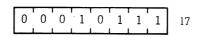

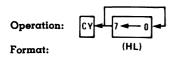

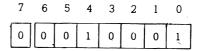

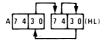

| RLD               | Rotate digit left and right between Acc. and location (HL) | 160 |

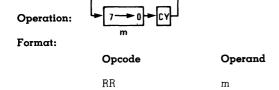

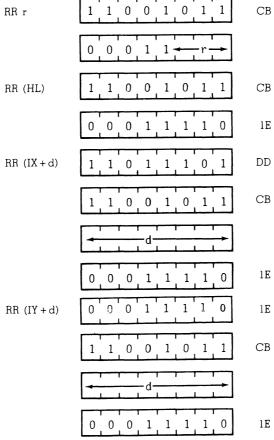

| RR m              | Rotate right through carry operand m                       | 162 |

| RRA               | Rotate right Acc. through carry                            | 164 |

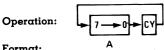

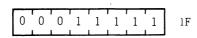

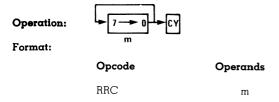

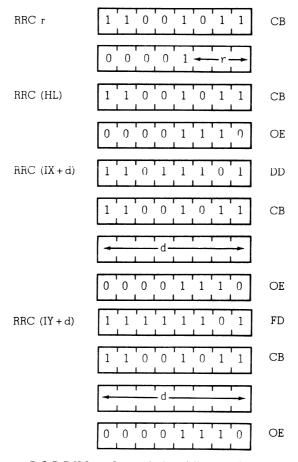

| RRC m             | Rotate operand m right circular                            | 165 |

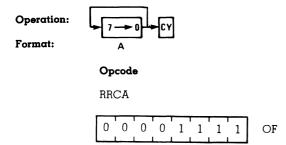

| RRCA              | Rotate right circular Acc                                  | 167 |

| RRD               | Rotate digit right and left between Acc. and location (HL) | 168 |

| RST p             | Restart to location p                                      | 170 |

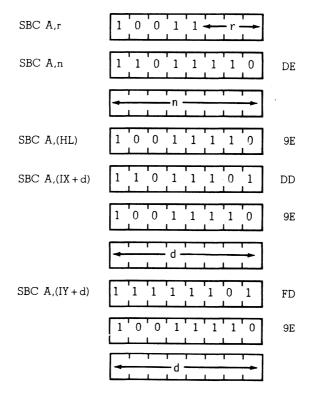

| SBC A, s          | Subtract operand s from Acc. with carry                    | 171 |

| SBC HL, ss        | Subtract Reg. pair ss from HL with carry                   | 173 |

| SCF               | Set carry flag $(C = 1)$                                   | 174 |

| SET b, (HL)       | Set Bit b of location (HL)                                 | 175 |

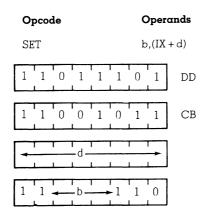

| SET b, $(IX + d)$ | Set Bit b of location (IX + d)                             | 176 |

| SET b, $(IY + d)$ | Set Bit b of location (IY + d)                             | 177 |

| SET b, r          | Set Bit b of Reg. r                                        | 178 |

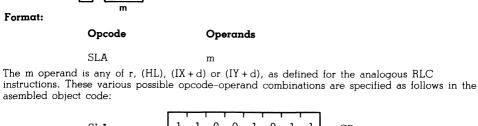

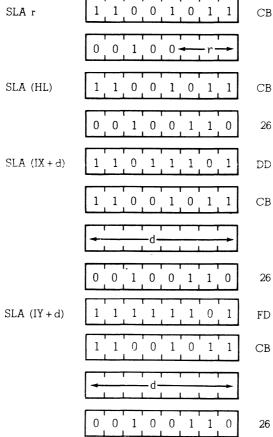

| SLA m             | Shift operand m left arithmetic                            | 179 |

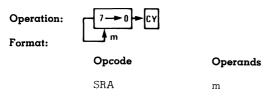

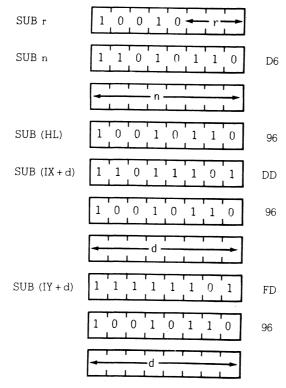

| SRA m             | Shift operand m right arithmetic                           | 181 |

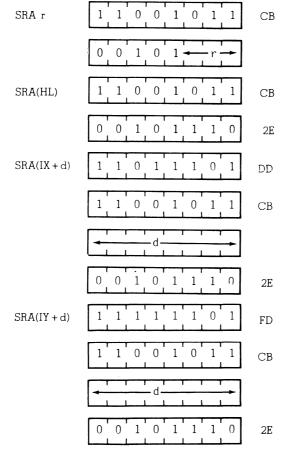

| SRL m             | Shift operand m right logical                              | 183 |

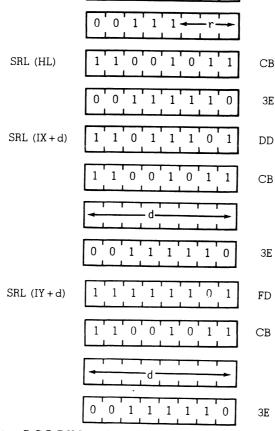

| SUB s             | Subtract operand s from Acc                                | 185 |

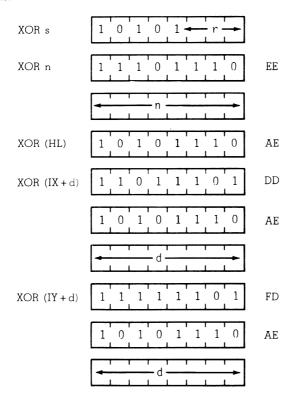

| XOR s             | Exclusive 'OR' operand s and Acc                           | 187 |

## **Execution Times**

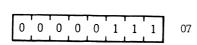

The execution time (E.T.) for each instruction is given in microseconds for an assumed 4 MHz clock. Total machine cycles (M) are indicated with total clock periods (T States). Also indicated are the number of T States for each M cycle. For example:

M CYCLES: 2 T STATES: 7 (4,3) 4 MHz E.T.: 1.75

indicates that the instruction consists of 2 machine cycles. The first cycle contains 4 clock periods (T States). The second cycle contains 3 clock periods for a total of 7 clock periods or T States. The instruction will execute in 1.75 microseconds.

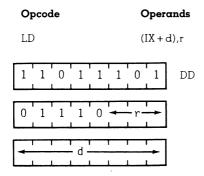

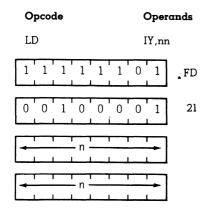

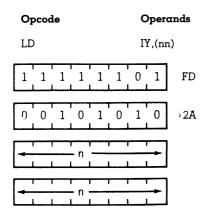

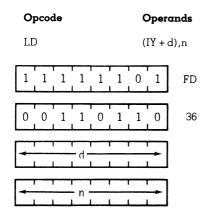

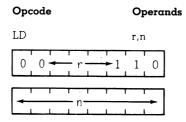

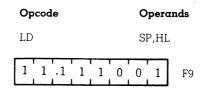

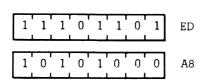

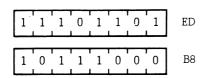

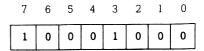

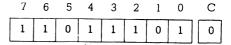

Register format is shown for each instruction with the most significant bit to the left and the least significant bit to the right.

# **Z80° PROGRAMMING MANUAL**

This manual contains a complete statement of the Z80 CPU instruction set. Each instruction is described by the operation, assembler mnemonic format op code. A description of the instruction operation is followed by the execution time with M cycles and T states, the flag status and, finally, an example of the instruction operation.

SGS will be grateful to receive from users information about any errors for points that are not clear in this manual which can be corrected in future editions.

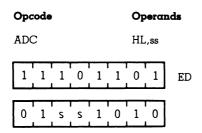

## ADC HL.ss

Operation:  $HL \leftarrow HL + ss + CY$

#### Format:

### Description:

The contents of register pair ss (any of register pairs BC, DE, HL or SP) are added with the Carry Flag (C flag in the F register) to the contents of register pair HL, and the result is stored in HL. Operand ss is specified as follows in the assembled object code.

| Register |    |

|----------|----|

| Pair     | 88 |

| ВС       | 00 |

| DE       | 01 |

| HL       | 10 |

| SP       | 11 |

M CYCLES: 4 T STATES: 15 (4,4,4,3) 4 MHz E.T.: 3.75

### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero;

reset otherwise

H: Set if carry out of

Bit 11; reset otherwise P/V: Set if overflow;

reset otherwise

N: Reset

C: Set if carry from

Bit 15; reset otherwise

#### Example:

If the register pair BC contains 2222H, register pair HL contains 5437H and the Carry Flag is set, after the execution of

ADC HL.BC

the contents of HL will be 765AH.

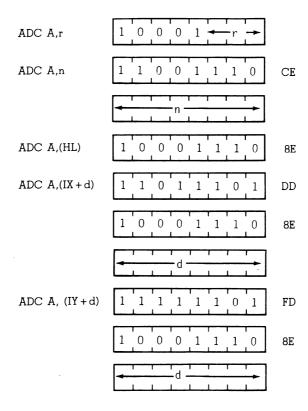

## ADC A,s

Operation:  $A \leftarrow A + s + CY$

Format:

| Opcode | Operands |

|--------|----------|

| ADC    | A,s      |

The s operand is any of r,n,(HL), (IX+d) or (IY+d) as defined for the analogous ADD instruction. These various possible opcode-operand combinations are assembled as follows in the object code:

r identifies registers B,C,D,E,H,L or A assembled as follows in the object code field above:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| L        | 101 |

| A        | 111 |

#### Description:

The s operand, along with the Carry Flag (C in the F register) is added to the contents of the Accumulator, and the result is stored in the Accumulator.

| INSTRUCTION        | M CYCLES | T STATES       | 4 MHz E.T.   |

|--------------------|----------|----------------|--------------|

| ADC A,r<br>ADC A,n | 1 2      | 4<br>7 (4,3)   | 1.00<br>1.75 |

| ADC A, (HL)        | 2        | 7 (4,3)        | 1.75         |

| ADC A, $(IX + d)$  | 5        | 19 (4,4,3,5,3) | 4.75         |

| ADC A, $(IY + d)$  | 5        | 19 (4,4,3,5,3) | 4.75         |

#### Condition Bits Affected:

S: Set if result is negative:

reset otherwise

7.: Set if result is zero:

reset otherwise Set if carry from

Bit 3; reset otherwise

Set if overflow;

P/V: reset otherwise

N: Reset

C: Set if carry from

Bit 7; reset otherwise

#### Example:

If the Accumulator contains 16H, the Carry Flag is set, the HL register pair contains 6666H, and address 6666H contains 10H, after the execution of

ADC A, (HL)

the Accumulator will contain 27H.

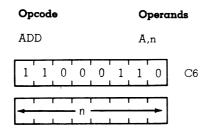

## ADD A,n

Operation:  $A \leftarrow A + n$

#### Format:

## Description:

The integer n is added to the contents of the Accumulator and the results are stored in the Accumulator.

M CYCLES: 2 T STATES: 6 (4,3) 4 MHz E.T.: 1.75

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero;

reset otherwise H: Set if carry from

Bit 3; reset otherwise

P/V: Set if overflow; reset otherwise

N: Reset

C: Set if carry from

Bit 7: reset otherwise

## Example:

If the contents of the Accumulator are 23H, after the execution of

ADD A,33H

the contents of the Accumulator will be 56H.

## ADD A.r

Operation:  $A \leftarrow A + r$

#### Format:

| Opcode |    |    |   |   | Or | er       | ands             |   |  |

|--------|----|----|---|---|----|----------|------------------|---|--|

|        | ΑI | DD |   |   |    |          | <b>A</b> ,:      | r |  |

|        | 1  | 0  | 0 | 0 | 0  | <b>—</b> | - r <del>-</del> | - |  |

#### Description:

The contents of register r are added to the contents of the Accumulator, and the result is stored in the Accumulator. The symbol r identifies the registers A,B,C,D,E,H or L assembled as follows in the object code:

| Register | r   |

|----------|-----|

| A        | 111 |

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| T        | 101 |

M CYCLES: 1 T STATES: 4 4 MHz E.T.: 1.00

## Conditions Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero; reset otherwise

H: Set if carry from Bit 3; reset otherwise

P/V: Set if overflow; reset otherwise

N: Reset

C: Set if carry from

Bit 7; reset otherwise

#### Example:

If the contents of the Accumulator are 44H, and the contents of register C are 11H, after the execution of

ADD A,C

the contents of the Accumulator will be 55H.

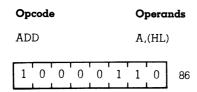

# ADD A,(HL)

Operation:  $A \leftarrow A + (HL)$

#### Format:

#### Description:

The byte at the memory address specified by the contents of the HL register pair is added to the contents of the Accumulator and the result is stored in the Accumulator.

M CYCLES: 2 T STATES: 7 (4,3) 4 MHz E.T.: 1.75

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero:

reset otherwise

H: Set if carry from

Bit 3; reset otherwise

P/V: Set if overflow;

reset otherwise

N: Reset

C: Set if carry from

Bit 7: reset otherwise

#### Example:

If the contents of the Accumulator are AOH, and the content of the register pair HL is 2323H, and memory location 2323H contains byte 08H, after the execution of

the Accumulator will contain A8H.

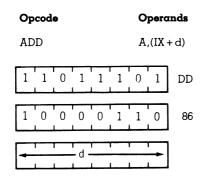

# ADD $A_{i}(IX+d)$

Operation:  $A \leftarrow A + (IX + d)$

#### Format:

### Description:

The contents of the Index Register (register pair IX) is added to a displacement d to point to an address in memory. The contents of this address is then added to the contents of the Accumulator and the result is stored in the Accumulator.

M CYCLES: 5 STATES: 19(4,4,3,5,3) 4 MHz E.T.: 4.75

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero;

reset otherwise

H: Set if carry from

Bit 3; reset otherwise

P/V: Set if overflow; reset otherwise

N: Reset

v: Reset

C: Set if carry from

Bit 7; reset otherwise

### Example:

If the Accumulator contents are 11H, the Index Register IX contains 1000H, and if the content of memory location 1005H is 22H, after the execution of

ADD

$$A_{i}(IX + 5H)$$

the contents of the Accumulator will be 33H.

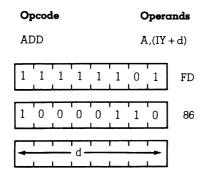

# ADD A(IY+d)

Operation:  $A \leftarrow A + (IY + d)$

#### Format:

## Description:

The contents of the Index Register (register pair IY) is added to a displacement d to point to an address in memory. The contents of this address is then added to the contents of the Accumulator and the result is stored in the Accumulator.

M CYCLES: 5 T STATES: 19(4,4,3,5,3) 4 MHz E.T.: 4.75

#### Condition Bits Affected:

S: Set if result is negative; reset otherwise

Z: Set if result is zero;

reset otherwise

H: Set if carry from

H: Set if carry from Bit 3; reset otherwise

P/V: Set if overflow; reset otherwise

N: Reset

C: Set if carry from bit 7;

reset otherwise

#### Example:

If the Accumulator contents are 11H, the Index Register pair IY contains 1000H, and if the content of memory location 1005H is 22H, after the execution of

$$ADD A_{1}(IY + 5H)$$

the contents of the Accumulator will be 33H.

# ADD HL,ss

Operation: HL←HL+ss

#### Format:

| Opcode      | Operands |

|-------------|----------|

| ADD         | HL,ss    |

| 0 0 s s 1 ( | 0 0 1    |

### Description:

The contents of register pair ss (any of register BC,DE,HL or SP) are added to the contents of register pair HL and the result is stored in HL. Operand ss is specified as follows in the assembled object code.

| Register<br>Pair | SS |

|------------------|----|

| ВС               | 00 |

| DE               | 01 |

| HL               | 10 |

| SP               | 11 |

M CYCLES: 3 T STATES: 11(4,4,3) 4 MHz E.T.: 2.75

## Condition Bits Affected:

S: Not affected

Z: Not affected

H: Set if carry out of Bit 11: reset otherwise

P/V: Not affected

N: Reset

C: Set if carry from

Bit 15; reset otherwise

### Example:

If register pair HL contains the integer 4242H and register pair DE contains 1111H, after the execution of

ADD HL, DE

the HL register pair will contain 5353H.

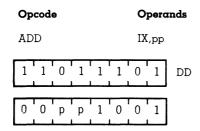

# ADD IX,pp

Operation:  $IX \leftarrow IX + pp$

Format:

### Description:

The contents of register pair pp (any of register pairs BC,DE,IX or SP) are added to the contents of the Index Register IX, and the results are stored in IX. Operand pp is specified as follows in the assembled object code.

| Register<br>Pair | pp             |

|------------------|----------------|

| BC<br>DE<br>IX   | 00<br>01<br>10 |

| SP               | 11             |

M CYCLES: 4 T STATES: 15(4,4,4,3) 4 MHz E.T.: 3.75

#### Condition Bits Affected:

S: Not affected

Z: Not affected

H: Set if carry out of Bit 11; reset otherwise

P/V: Not affected

N: Reset

C: Set if carry from

Bit 15; reset otherwise

#### Example:

If the contents of Index Register IX are 3333H and the contents of register pair BC are 5555H, after the execution of

ADD IX,BC

the contents of IX will be 8888H.

## ADD IY,rr

Operation:  $IY \leftarrow IY + rr$

#### Format:

| Opcode | Operands |       |    |  |

|--------|----------|-------|----|--|

| ADD    |          | IY,rr |    |  |

| 1 1 1  | 1 1 1    | 0 1   | FD |  |

| 0 0 r  | r 1 0    | 0 1   |    |  |

## Description:

The contents of register pair rr (any of register pairs BC,DE,IY or SP) are added to the contents of Index Register IY, and the result is stored in IY. Operand rr is specified as follows in the assembled object code.

| Register<br>Pair | rr |

|------------------|----|

| ВС               | 00 |

| DE               | 01 |

| IY               | 10 |

| SP               | 11 |

M CYCLES: 4 T STATES: 15(4,4,4,3) 4 MHz E.T.: 3.75

#### Condition Bits Affected:

S: Not affected

Z: Not affected

H: Set if carry out of Bit 11; reset otherwise

P/V: Not affected

N: Reset

C: Set if carry from

Bit 15; reset otherwise

## Example:

If the contents of Index Register IY are 3333H and the contents of register pair BC are 5555H, after the execution of

ADD IY, BC

the contents of IY will be 8888H.

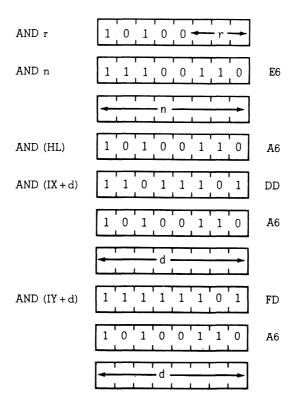

## AND s

Operation:  $A \leftarrow A \land s$

Format:

| Opcode | Operands |

|--------|----------|

| AND    | s        |

The s operand is any of r,n,(HL),(IX+d) or (IY+d), as defined for the analogous ADD instructions. These various possible opcode-operand combinations are assembled as follows in the object code:

r identifies registers B,C,D,E,H,L or A assembled as follows in the object code field above:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| L        | 101 |

| A        | 111 |

## Description:

A logical AND operation, bit by bit, is performed between the byte specified by the s operand and the byte contained in the Accumulator; the result is stored in the Accumulator.

| INSTRUCTION | M CYCLES | T STATES      | 4 MHz E.T. |

|-------------|----------|---------------|------------|

| AND r       | 1        | 4             | 1.00       |

| AND n       | 2        | 7(4,3)        | 1.75       |

| AND (HL)    | 2        | 7(4,3)        | 1.75       |

| AND (IX+d)  | 5        | 19(4,4,3,5,3) | 4.75       |

| AND (IX+d)  | 5        | 19(4,4,3,5,3) | 4.75       |

## Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero:

reset otherwise

H: Set

Set if parity even; P/V:

reset otherwise

Reset Reset C:

## Example:

If the B register contains 7BH (01111011) and the Accumulator contains C3H (11000011) after the execution of

AND B

the Accumulator will contain 43H (01000011).

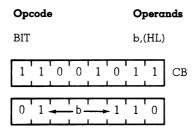

# BIT b,(HL)

Operation:  $Z \leftarrow (\overline{HL})_b$

#### Format:

## Description:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the contents of the HL register pair. Operand b is specified as follows in the assembled object code:

| Bit Tested | b   |

|------------|-----|

| 0          | 000 |

| l          | 001 |

| 2          | 010 |

| 2<br>3     | 011 |

| 4          | 100 |

| 5          | 101 |

| 6          | 110 |

| 7          | 111 |

M CYCLES: 3

T STATES: 12(4,4,4)

4 MHz E.T.: 3.00

#### Condition Bits Affected:

S: Unknown

Z: Set if specified Bit is

0; reset otherwise

H: Set

P/V: Unknown

N: Reset

C: Not affected

#### Example:

If the HL register pair contains 4444H, and bit 4 in the memory location 4444H contains 1, after the execution of

the Z flag in the F register will contain 0, and bit 4 in memory location 4444H will still contain 1.

# BIT b(IX+d)

Operation:  $Z \leftarrow \overline{(IX + d)}_b$

#### Format:

| Opcode |        |     |   |          | 0 | pera     | nds  |

|--------|--------|-----|---|----------|---|----------|------|

| BIT    |        |     |   |          | b | + XI),   | - d) |

| 1 1    | 0      | 1   | 1 | 1        | 0 | 1        | DD   |

| 1 1    | 0      | 0   | 1 | 0        | 1 | 1        | СВ   |

|        | ·      | -d- |   | <u> </u> | r | <u> </u> |      |

| 0 1    | 1<br>4 | -b- |   | - 1      | 1 | 0        |      |

### Description:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the contents of the memory location pointed to by the sum of the contents register pair IX (Index Register IX) and the two's complement displacement integer d. Operand b is specified as follows in the assembled object code.

| Bit Tested | b   |

|------------|-----|

| 0          | 000 |

| 1          | 001 |

| 2          | 010 |

| 3          | 011 |

| 4          | 100 |

| 5          | 101 |

| 6          | 110 |

| 7          | 111 |

M CYCLES: 5 T STATES: 20(4,4,3,5,4) 4 MHz E.T.: 5.

#### Condition Bits Affected:

S: Unknown

Z: Set if specified Bit is

0; reset otherwise

H: Set

P/V: Unknown

N: Reset

C: Not affected

# BIT b(IX+d)

## Example:

If the contents of Index Register IX are 2000H, and bit 6 in memory location 2004H contains l, after the execution of

BIT 6, (IX + 4H)

the Z flag in the F register will contain 0, and bit 6 in memory location 2004H will still contain 1.

Operation:  $Z \leftarrow \overline{(IY + d)}_b$

#### Format:

| Opcode Ope |     |          |     |   | pero | nds |         |      |

|------------|-----|----------|-----|---|------|-----|---------|------|

| ВІТ        | •   |          |     |   |      | b   | ,(IY +  | - d) |

| 1          | 1   | 1        | 1   | 1 | 1    | 0   | 1       | FD   |

| 1          | 1   | 0        | 0   | 1 | 0    | 1   | 1       | СВ   |

| -          |     | <u> </u> | d-  |   | · ·  | T   | <u></u> |      |

| 0          | 1 . |          | _b_ |   | 1    | 1   | 0       |      |

## Description:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the contents of the memory location pointed to by the sum of the contents of register pair IY (Index Register IY) and the two's complement displacement integer d. Operand b is specified as follows in the assembled object code:

| Bit Tested | b   |

|------------|-----|

| 0          | 000 |

| 1          | 001 |

| 2          | 010 |

| 2<br>3     | 011 |

| 4          | 100 |

| 5          | 101 |

| 6          | 110 |

| 7          | 111 |

M CYCLES: 5 T STATES: 20(4,4,3,5,4) 4 MHz E.T.: 5.00

#### Condition Bits Affected:

S: Unknown

Z: Set if specified Bit is 0: reset otherwise

Set

H: Se

P/V: Unknown

N: Reset

C: Not affected

# BIT b(IY+d)

## Example:

If the contents of Index Register IY are 2000H, and bit 6 in memory location 2004H contains 1, after the execution of

BIT 6, (IY + 4H)

the Z flag in the F register still contain 0, and bit 6 in memory location 2004H will still contain 1.

Operation:  $Z \leftarrow \bar{r}_b$

#### Format:

| Opcode |       | Opero          | ınds |

|--------|-------|----------------|------|

| BIT    |       | b,r            |      |

| 1 1 0  | 0 1 0 | 1 1            | СВ   |

| 0 1    | -b-   | -r <del></del> |      |

## Description:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the indicated register. Operands b and r are specified as follows in the assembled object code:

| Bit tested | b   | Register | r   |

|------------|-----|----------|-----|

| 0          | 000 | В        | 000 |

| l          | 001 | С        | 001 |

| 2          | 010 | D        | 010 |

| 3          | 011 | E        | 011 |

| 4          | 100 | Н        | 100 |

| 5          | 101 | L        | 101 |

| 6          | 110 | A        | 111 |

| 7          | 111 |          |     |

M CYCLES: 2 T STATES: 8(4,4) 4 MHz E.T.: 2.00

#### Condition Bits Affected:

S: Unknown

Z: Set if specified Bit is

0; reset otherwise

H: Set

P/V: Unknown

N: Reset

C: Not affected

## Example:

If bit 2 in register B contains 0, after the execution of

RIT 2 R

the Z flag in the F register will contain 1, and bit 2 in register B will remain 0.

#### CALL cc,nn

$\begin{aligned} \textbf{Operation:} \ \text{IF cc TRUE:} \ (SP\text{--}1) \leftarrow & PC_H \\ (SP\text{--}2) \leftarrow & PC_{L'} \ PC \leftarrow & nn \end{aligned}$

Format:

| Opcode            | Operands         |

|-------------------|------------------|

| CALL              | cc,nn            |

| 1 1 <del>cc</del> | 1 0 0            |

| → n —             | <b> </b>         |

| - n               | ↑ ↑ ↑<br>↓ ↓ ↓ ↓ |

Note: The first of the two n operands in the assembled object code above is the least significant byte of the two-byte memory address.

#### Description:

If condition cc is true, this instruction pushes the current contents of the Program Counter (PC) onto the top of the external memory stack, then loads the operands nn into PC to point to the address in memory where the first opcode of a subroutine is to be fetched. (At the end of the subroutine, a RETurn instruction can be used to return to the original program flow by popping the top of the stack back into PC.) If condition cc is false, the Program Counter is incremented as usual, and the program continues with the next sequential instruction. The stack push is accomplished by first decrementing the current contents of the Stack Pointer (SP), loading the high-order byte of the PC contents into the memory address now pointed to by SP; then decrementing SP again, and loading the low-order byte of the PC contents into the top of the stack. Note: Because this is a 3-byte instruction, the Program Counter will have been incremented by 3 before the push is executed. Condition cc is programmed as one of eight status which corresponds to condition bits in the Flag Register (register F). These eight status are defined in the table below, which also specifies the corresponding cc bit fields in the assembled object code:

| CC         | Condition                          | Relevant<br>Flag |

|------------|------------------------------------|------------------|

| 000<br>001 | NZ non zero<br>Z zero              | Z<br>Z           |

| 010        | NC non carry                       | С                |

| 011<br>100 | C carry<br>PO parity odd           | C<br>P/V         |

| 101<br>110 | PE parity even                     | P/V              |

| 111        | P sign positive<br>M sign negative | S<br>S           |

## CALL cc,nn

If cc is true:

M CYCLES: 5 T STATES: 17(4,3,4,3,3) 4 MHz E.T.: 4.25

If cc is false:

M CYCLES: 3 T STATES: 10(4,3,3) 4 MHz E.T.: 2.50

Condition Bits Affected: None

#### Example:

If the C Flag in the F register is reset, the contents of the Program Counter are 1A47H, the contents of the Stack Pointer are 3002H, and memory locations have the contents:

| Location      | Contents |  |

|---------------|----------|--|

| 1A47H         | D4H      |  |

| 1A48H         | 35H      |  |

| 1 <b>A49H</b> | 21H      |  |

then if an instruction fetch sequence begins, the three-byte instruction D43521H will be fetched to the CPU for execution. The mnemonic equivalent of this is

CALL NC,2135H

After the execution of this instruction, the contents of memory address 3001H will be 1AH, the contents of address 3000H will be 4AH, the contents of the Stack Pointer will be 3000H, and the contents of the Program Counter will be 2135H, pointing to the address of the first opcode of the subroutine now to be executed.

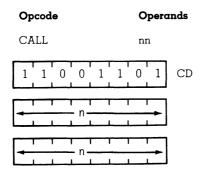

## CALL nn

$\textbf{Operation:} \ (SP-1) \leftarrow PC_{H'} \ \ (SP-2) \leftarrow PC_{L'} \ \ PC \leftarrow nn$

Format:

Note: The first of the two n operands in the assembled object code above is the least significant byte of a two-byte memory address.

## Description:

After pushing the current contents of the Program Counter (PC) onto the top of the external memory stack, the operands nn are loaded into PC to point to the address in memory where the first opcode of a subroutine is to be fetched. (At the end of the subroutine, a RETurn instruction can be used to return to the original program flow by popping the top of the stack back into PC.) The push is accomplished by first decrementing the current contents of the Stack Pointer (register pair SP), loading the high-order byte of the PC contents into the memory address now pointed to by the SP; then decrementing SP again, and loading the low-order byte of the PC contents into the top of stack. Note: Because this is a 3-byte instruction, the Program Counter will have been incremented by 3 before the push is executed.

M CYCLES: 5 T STATES: 17(4,3,4,3,3) 4 MHz E.T.: 4.2

Condition Bits Affected: None

## CALL nn

#### Example:

If the contents of the Program Counter are 1A47H, the contents of the Stack Pointer are 3002H, and memory locations have the contents:

| Location       | Contents |

|----------------|----------|

| 1 <b>A</b> 47H | CDH      |

| 1 <b>Ā48H</b>  | 35H      |

| 1 <b>A</b> 49H | 21H      |

then if an instruction fetch sequence begins, the three-byte instruction CD3521H will be fetched to the CPU for execution. The mnemonic equivalent of this is

#### CALL 2135H

After the execution of this instruction, the contents of memory address 3001H will be 1AH, the contents of address 3000H will be 4AH, the contents of the Stack Pointer will be 3000H, and the contents of the Program Counter will be 2135H, pointing to the address of the first opcode of the subroutine now to be executed.

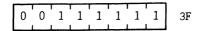

## **CCF**

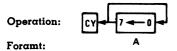

Operation:  $CY \leftarrow \overline{CY}$

Format:

## Opcode

CCF

## Description:

The C flag in the F register is inverted.

M CYCLES: 1 T STATES: 4 4 MHz E.T.: 1.00

### Condition Bits Affected:

S: Not affected

Z: Not affected

H: Previous carry will be copied

P/V: Not affected

N: Reset

C: Set if CY was 0 before

operation; reset otherwise

## Operation: A-s

## Format:

| Opcode | Operands |

|--------|----------|

| CP     | s        |

The s operand is any of r,n(HL),(IX+d) or (IY+d), as defined for the analogous ADD instructions. These various possible opcode-operand combinations are assembled as follows in the object code:

| CP r      | 1 0 1 1 1 + r   |    |

|-----------|-----------------|----|

| CP n      | 1 1 1 1 1 1 0   | FE |

|           | n               |    |

| CP (HL)   | 1 0 1 1 1 1 1 0 | BE |

| CP (IX+d) | 1 1 0 1 1 1 0 1 | DD |

|           | 1 0 1 1 1 1 0   | BE |

|           | <b>←</b>        |    |

| CP (IY+d) | 1 1 1 1 1 0 1   | FD |

|           | 1 0 1 1 1 1 0   | BE |

|           | <b>←</b> d      |    |

r identifies registers B,C,D,E,H,L or A assembled as follows in the object code field above:

## CP s

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| H        | 100 |

| L        | 101 |

| A        | 111 |

## Description:

The contents of the s operand are compared with the contents of the Accumulator. If there is a true compare, a flag is set.

| INSTRUCTION | M CYCLES | T STATES      | 4 MHz E.T. |

|-------------|----------|---------------|------------|

| CP r        | 1        | 4             | 1.00       |

| CP n        | 2        | 7(4,3)        | 1.75       |

| CP (HL)     | 2        | 7(4,3)        | 1.75       |

| CP (IX + d) | 5        | 19(4,4,3,5,3) | 4.75       |

| CP (IY + d) | 5        | 19(4,4,3,5,3) | 4.75       |

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero;

reset otherwise

H: Set in there is a borrow

and reset otherwise.

P/V: Set if overflow;

reset otherwise

N: Set

C: Set if there is a borrow

and reset otherwise.

#### Example:

If the Accumulator contains 63H, the HL register pair contains 6000H and memory location 6000H contains 60H, the instruction

CP (HL)

will result in the P/V flag in the F register being reset.

Operation: A-(HL),  $HL\leftarrow HL-1$ ,  $BC\leftarrow BC-1$

#### Format:

#### Opcode

CPD

### Description:

The contents of the memory location addressed by the HL register pair is compared with the contents of the Accumulator. In case of a true compare, a condition bit is set. The HL and the Byte Counter (register pair BC) are decremented.

M CYCLES: 4 T STATES: 16(4,4,3,5) 4 MHz E.T.: 4.00

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

7.: Set if A = (HL):

reset otherwise

H: Set if there is a borrow and reset otherwise.

Set if  $BC-1 \neq 0$ :

P/V: reset otherwise

> N: Set

C: Not Affected

#### Example:

If the HL register pair contains 1111H, memory location 1111H contains 3BH, the Accumulator contains 3BH, and the Byte Counter contains 0001H, then after the execution of

CPD

the Byte Counter will contain 0000H, the HL register pair will contain 1110H, the Z flag in the Fregister will be set, and the P/V flag in the F register will be reset. There will be no effect on the contents of the Accumulator or address 1111H.

## **CPDR**

Operation: A - (HL), HL←HL-1, BC←BC-1

#### Format:

### Opcode

**CPDR**

#### Description:

The contents of the memory location addressed by the HL register pair is compared with the contents of the Accumulator. In case of a true compare, a condition bit is set. The HL and BC (Byte Counter) register pairs are decremented. If decrementing causes the BC to go to zero or if A = (HL), the instruction is terminated. If BC is not zero and  $A \neq (HL)$ , the program counter is decremented by 2 and the instruction is repeated. Note that if BC is set to zero prior to instruction execution, the instruction will loop through 64K bytes, if no match is found. Interrupts will be recognized and two refresh cycles will be executed after each data transfer.

For BC  $\neq$  0 and A  $\neq$  (HL):

M CYCLES: 5 T STATES: 21(4,4,3,5,5) 4 MHz E.T.: 5.25

For BC = 0 or A = (HL):

M CYCLES: 4 T STATES: 16(4,4,3,5) 4 MHz E.T.: 4.00

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if A = (HL); reset otherwise

H: Set if there is a borrow and reset otherwise.

P/V: Set if BC-1≠0;

reset otherwise N: Set

C: Not affected

## Example:

If the HL register pair contains 1118H, the Accumulator contains F3H, the Byte Counter contains 0007H, and memory locations have these contents:

(1118H): 52H (1117H): 00H (1116H): F3H

then after the execution of

**CPDR**

the contents of register pair HL will be 1115H, the contents of the Byte Counter will be 0004H, the P/V flag in the F register will be set, and the Z flag in the F register will be set.

Operation: A - (HL),  $HL\leftarrow HL+1$ ,  $BC\leftarrow BC-1$

#### Format:

## Opcode

CPI

#### Description:

The contents of the memory location addressed by the HL register pair is compared with the contents of the Accumulator. In case of a true compare, a condition bit is set. Then HL is incremented and the Byte Counter (register pair BC) is decremented.

M CYCLES: 4 T STATES: 16(4,4,3,5) 4 MHz E.T.: 4.00

#### Condition Bits Affected:

S: Set if result is negative; reset otherwise

Z: Set if A = (HL); reset otherwise

H: Set if there is a borrow

and reset otherwise. P/V: Set if  $BC-1 \neq 0$ :

P/V: Set if BC-1≠0; reset otherwise

N: Set

C: Not affected

## Example:

If the HL register pair contains 1111H, memory location 1111H contains 3BH, the Accumulator contains 3BH, and the Byte Counter contains 0001H, then after the execution of

CPI

the Byte Counter will contain 0000H, the HL register pair will contain 1112H, the Z flag in the F register will be set, and the P/V flag in the F register will be reset. There will be no effect on the contents of the Accumulator or address 1111H.

Operation: A - (HL),  $HL \leftarrow HL + 1$ ,  $BC \leftarrow BC - 1$

#### Format:

#### Opcode

**CPIR**

## Description:

The contents of the memory location addressed by the HL register pair is compared with the contents of the Accumulator. In case of a true compare, a condition bit is set. The HL is incremented and the Byte Counter (register pair BC) is decremented. If decrementing causes the BC to go to zero or if A = (HL), the instruction is terminated. If BC is not zero and  $A \neq (HL)$ , the program counter is decremented by 2 and the instruction is repeated. Note that if BC is set to zero before instruction execution, the instruction will loop through 64K bytes, if no match is found. Interrupts will be recognized and two refresh cycles will be executed after each data transfer.

For  $BC \neq 0$  and  $A \neq (HL)$ :

M CYCLES: 5 T STATES: 21(4,4,3,5,5) 4 MHz E.T.: 5.25

For BC = 0 or A = (HL):

M CYCLES: 4 T STATES: 16(4,4,3,5) 4 MHz E.T.: 4.00

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if A = (HL); reset otherwise

H: Set if there is a borrow and reset otherwise.

P/V: Set if BC-1 $\neq$ 0;

reset otherwise

N: Set

C: Not affected

## **CPIR**

## Example:

If the HL register pair contains 1111H, the Accumulator contains F3H, the Byte Counter contains 0007H, and memory locations have these contents:

(1111H): 52H (1112H): 00H (1113H): F3H

then after the execution of

**CPIR**

the contents of register pair HL will be 1114H, the contents of the Byte Counter will be 0004H, the P/V flag in the F register will be set and the Z flag in the F register will be set.

Operation:  $A \leftarrow \overline{A}$

#### Format:

#### Opcode

CPL

## Description:

Contents of the Accumulator (register A) are inverted (1's complement).

M CYCLES: 1 T STATES: 4 4 MHz E.T.: 1.00

#### Condition Bits Affected:

S: Not affected

Z: Not affected

H: Set

P/V: Not affected

N: Set

C: Not affected

## Example:

If the contents of the Accumulator are 1011 0100, after the execution of CPI.

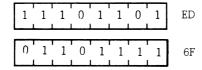

the Accumulator contents will be 0100 1011.

## DAA

Operation: Decimal Adjust Accumulator

Format:

## Opcode

DAA

## Description:

This instruction conditionally adjusts the Accumulator for BCD addition and subtraction operations. For addition (ADD, ADC, INC) or subtraction (SUB, SBC, DEC, NEG), the following table indicates operation performed:

| OPERATION                | C<br>BEFORE<br>DAA                        | HEX<br>VALUE<br>IN<br>UPPER<br>DIGIT<br>(bit<br>7-4)                              | H<br>Before<br>Daa                   | HEX<br>VALUE<br>IN<br>LOWER<br>DIGIT<br>(bit<br>3-0)        | NUMBER<br>ADDED<br>TO<br>BYTE                      | C<br>AFTER<br>DAA                    |

|--------------------------|-------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------|----------------------------------------------------|--------------------------------------|

| ADD<br>ADC<br>INC        | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1 | 0-9<br>0-8<br>0-9<br><b>A-F</b><br>9- <b>F</b><br><b>A-F</b><br>0-2<br>0-2<br>0-3 | 0<br>0<br>1<br>0<br>0<br>1<br>0<br>0 | 0-9<br>A-F<br>0-3<br>0-9<br>A-F<br>0-3<br>0-9<br>A-F<br>0-3 | 00<br>06<br>06<br>60<br>66<br>66<br>60<br>66<br>66 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 |

| SUB<br>SBC<br>DEC<br>NEG | 0<br>0<br>1<br>1                          | 0-9<br>0-8<br>7-F<br>6-F                                                          | 0<br>1<br>0<br>1                     | 0-9<br>6-F<br>0-9<br>6-F                                    | 00<br>FA<br>A0<br>9A                               | 0<br>0<br>1<br>1                     |

M CYCLES: 1 T STATES: 4 4 MHz E.T.: 1.00

#### Condition Bits Affected:

Set if most significant bit of Acc. is 1 after operation;

reset otherwise

Z: Set if Acc. is zero after operation;

reset otherwise

H: See instruction

P/V: Set if Acc. is even parity after

operation; reset otherwise

N: Not affected

C: See instruction

## Example:

If an addition operation is performed between 15 (BCD) and 27 (BCD), simple decimal arithmetic gives this result:

$$\frac{15}{+27}$$

But when the binary representations are added in the Accumulator according to standard binary arithmetic,

the sum is ambiguous. The DAA instruction adjusts this result so that the correct BCD representation is obtained:

$$\begin{array}{c|ccc}

0011 & 1100 \\

+0000 & 0110 \\

\hline

0100 & 0010 = 42

\end{array}$$

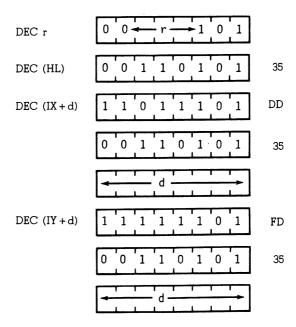

## DEC m

Operation: m - m-l

Format:

| Opcode | Operands |

|--------|----------|

| DEC    | m        |

The m operand is any of r, (HL), (IX+d) or (IY+d), as defined for the analogous INC instructions. These various possible opcode-operand combinations are assembled as follows in the object code:

r identifies registers B,C,D,E,H,L or A assembled as follows in the object code field above:

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| Ε        | 011 |

| H        | 100 |

| L        | 101 |

| A        | 111 |

## Description:

The byte specified by the m operand is decremented.

| INSTRUCTION | M CYCLES | T STATES        | 4 MHz E.T. |

|-------------|----------|-----------------|------------|

| DEC r       | 1        | 4               | 1.00       |

| DEC (HL)    | 3        | 11(4,4,3)       | 2.75       |

| DEC (IX+d)  | 6        | 23(4,4,3,5,4,3) | 5.75       |

| DEC (IY+d)  | 6        | 23(4,4,3,5,4,3) | 5.75       |

#### Condition Bits Affected:

S: Set if result is negative;

reset otherwise

Z: Set if result is zero;

reset otherwise

H: Set if there is a borrow and reset otherwise.

P/V: Set if m was 80H before

operation; reset otherwise

N: Set

C: Not affected

## Example:

If the D register contains byte 2AH, after the execution of

DEC D

register D will contain 29H.

# DEC IX

Operation:  $IX \leftarrow IX-1$

## Format:

| Opcode Oper     | Operands |  |  |  |

|-----------------|----------|--|--|--|

| DEC IX          |          |  |  |  |

| 1 1 0 1 1 1 0 1 | DD       |  |  |  |

| 0 0 1 0 1 0 1 1 | 2B       |  |  |  |

## Description:

The contents of Index Register IX are decremented.

M CYCLES: 2 T STATES: 10(4,6) 4 MHz E.T.: 2.50

Condition Bits Affected: None

#### Example:

If the contents of Index Register IX are 2006H, after the execution of DEC IX  $\,$

the contents of Index Register IX will be 2005H.

# DEC IY

Operation:  $IY \leftarrow IY-1$

#### Format:

| Opcode Opera    | Operands |  |  |  |

|-----------------|----------|--|--|--|

| DEC IY          |          |  |  |  |

| 1 1 1 1 1 0 1   | FD       |  |  |  |

| 0 0 1 0 1 0 1 1 | 2B       |  |  |  |

## Description:

The contents of the Index Register IY are decremented.

M CYCLES: 2 T STATES: 10 (4,6) 4 MHz E.T.: 2.50

Condition Bits Affected: None

## Example:

If the contents of the Index Register IY are 7649H, after the execution of DEC IY

the contents of Index Register IY will be 7648H.

## DEC ss

Operation: ss-ss-l

#### Format:

| Opcode | Operand   | s |

|--------|-----------|---|

| DEC    | ss        |   |

| 0 0 s  | s 1 0 1 1 |   |

#### Description:

The contents of register pair ss (any of the register pairs BC,DE,HL or SP) are decremented. Operand ss is specified as follows in the assembled object code.

| Pair | SS |

|------|----|

| ВС   | 00 |

| DE   | 01 |

| HL   | 10 |

| SP   | 11 |

M CYCLES: 1

T STATES: 6 4 MHz E.T.: 1.50

Condition Bits Affected:

None

## Example:

If register pair HL contains 1001H, after the execution of DEC HL

the contents of HL will be 1000H.

Operation: IFF  $\leftarrow 0$

#### Format:

#### Opcode

DI

## Description:

DI disables the maskable interrupt by resetting the interrupt enable flip-flops (IFF1 and IFF2). Note that this instruction disables the maskable interrupt during its execution.

M CYCLES: 1 T STATES: 4 4 MHz E.T.: 1.00

Condition Bits Affected: None

## Example:

When the CPU executes the instruction

DI

the maskable interrupt is disabled until it is subsequently re-enabled by an EI instruction. The CPU will not respond to an Interrupt Request (INT) signal.

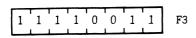

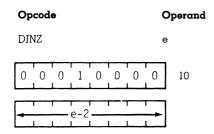

# DJNZ e

Operation: Jump relative and decrement.

#### Format:

#### Description:

This instruction is similar to the conditional jump instructions except that a register value is used to determine branching. The B register is decremented and if a non zero value remains, the value of the displacement e is added to the Program Counter (PC). The next instruction is fetched from the location designated by the new contents of the PC. The jump is measured from the address of the instruction opcode and has a range of -126 to +129 bytes. The assembler calculates the displacement e and automatically adjusts for the twice incremented PC. If the result of decrementing leaves B with a zero value, the next instruction to be executed is taken from the location following this instruction.

If  $B \neq 0$ :

M CYCLES: 3 T STATES: 13(5,3,5) 4 MHz E.T.: 3.25

If B≠0:

M CYCLES: 2 T STATES: 8(5,3) 4 MHz E.T.: 2.00

# DJNZ e

## Example:

A typical software routine is used to demonstrate the use of the DJNZ instruction. This routine moves a line from an input buffer (INBUF) to an output buffer (OUTBUF). It moves the bytes until it finds a CR, or until it has moved 80 bytes, whichever occurs first.

|       | LD<br>LD<br>LD | B,80<br>HL,INBUF<br>DE,OUTBUF | ; Set up counter<br>; Set up pointers |

|-------|----------------|-------------------------------|---------------------------------------|

| LOOP: | LD             | A,(HL)                        | ; Get next byte from ; input buffer   |

|       | LD             | (DE),A                        | ; Store in output buffer              |

|       | CP             | 0DH                           | ; Is it a CR?                         |

|       | JR             | Z,DONE                        | ; Yes finished                        |

|       | INC<br>INC     | HL<br>DE                      | ; Increment pointers                  |

|       | DINZ           | LOOP                          | ; Loop back if 80                     |

|       |                |                               | ; bytes have not                      |

|       |                |                               | ; been moved                          |

DONE:

Operation: IFF  $\leftarrow 1$

Format:

Opcode

ΕI

## Description:

EI enables the maskable interrupt by setting the interrupt enable flip-flops (IFF1 and IFF2). Note that this instruction disables the maskable interrupt during its execution.

M CYCLES: 1 T STATES: 4 4 MHz E.T.: 1.00

Condition Bits Affected: None

## Example:

When the CPU executes instruction

EI

the maskable interrupt is enabled. The  ${\ensuremath{\mathsf{CPU}}}$  will now respond to an Interrupt Request (INT) signal.

Operation:  $H \leftrightarrow (SP + 1)$ ,  $L \leftrightarrow (SP)$

#### Format:

| Opcode |    |   |   |   |   | 0 | perc | ınds |            |

|--------|----|---|---|---|---|---|------|------|------------|

|        | EX |   |   |   |   |   | (S   | P),F | IL         |

|        | 1  | 1 | 1 | 0 | 0 | 0 | 1    | 1    | <b>E</b> 3 |

#### Description:

The low order byte contained in register pair HL is exchanged with the contents of the memory address specified by the contents of register pair SP (Stack Pointer), and the high order byte of HL is exchanged with the next highest memory address (SP+1).

M CYCLES: 5 T STATES: 19(4,3,4,3,5) 4 MHz E.T.: 4.75

Condition Bits Affected: None

#### Example:

If the HL register pair contains 7012H, the SP register pair contains 8856H, the memory location 8856H contains the byte 11H, and the memory location 8857H contains the byte 22H, then the instruction

will result in the HL register pair containing number 2211H, memory location 8856H containing the byte 12H, the memory location 8857H containing the byte 70H and the Stack Pointer containing 8856H.

## EX (SP),IX

Operation:  $IX_H \leftrightarrow (SP + 1)$ ,  $IX_I \leftrightarrow (SP)$

Format:

| Opcode Operands |   |   |   |   |    | 3     |   |    |

|-----------------|---|---|---|---|----|-------|---|----|

| EX              |   |   |   |   | (S | SP),I | X |    |

| 1               | 1 | 0 | 1 | 1 | 1  | 0     | 1 | DD |

| 1               | 1 | 1 | 0 | 0 | 0  | 1     | 1 | ЕЗ |

## Description:

The low order byte in Index Register IX is exchanged with the contents of the memory address specified by the contents of register pair SP (Stack Pointer), and the high order byte of IX is exchanged with the next highest memory address (SP + 1).

M CYCLES: 6

T STATES: 23(4,4,3,4,3,5) 4 MHz E.T.: 5.75

Condition Bits Affected:

None

#### Example:

If the Index Register IX contains 3988H, the SP register pair contains 0100H, the memory location 0100H contains the byte 90H, and memory location 0101H contains byte 48H, then the instruction

will result in the IX register pair containing number 4890H, memory location 0100H containing 88H, memory location 0101H containing 39H and the Stack Pointer containing 0100H.

**Operation:**  $IY_H \leftrightarrow (SP + 1)$ ,  $IY_L \leftrightarrow (SP)$

#### Format:

| Opcode |   |   | Operands |   |   |    |       |            |

|--------|---|---|----------|---|---|----|-------|------------|

| EX     |   |   |          |   |   | (5 | SP),I | Y          |

| 1      | 1 | 1 | 1        | 1 | 1 | 0  | 1     | FD         |

| 1      | 1 | 1 | 0        | 0 | 0 | 1  | 1     | <b>E</b> 3 |

### Description:

The low order byte in Index Register IY is exchanged with the contents of the memory address specified by the contents of register pair SP (Stack Pointer), and the high order of IY is exchanged with the next highest memory address (SP+1).

M CYCLES: 6 T STATES: 23(4,4,3,4,3,5) 4 MHz E.T.: 5.75

Condition Bits Affected: None

## Example:

If the Index Register IY Contains 3988H, the SP register pair contains 0100H, the memory location 0100H contains the byte 90H, and memory location 0101H contains byte 48H, then the instruction

EX (SP), IY

will result in the IY register pair containing number 4890H, memory location 0100H containing 88H, memory location 0101H containing 39H, and the Stack Pointer containing 0100H.

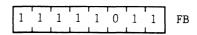

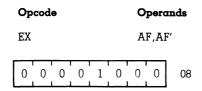

## EX AF, AF'

Operation:  $AF \leftrightarrow AF'$

#### Format:

## Description:

The two-byte contents of the register pairs AF and AF' are exchanged. (Note: register pair AF' consists of registers A' and F'.)

M CYCLES: 1

T STATES: 4

4 MHz E.T.: 1.00

Condition Bits Affected:

None

## Example:

If the content of register pair AF is number 9900H, and the content of register pair AF' is number 5944H, after the instruction

EX AF, AF'

the contents of AF will be 5944H, and the contents of AF' will be 9900H.

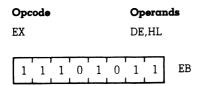

## EX DE,HL

Operation: DE↔HL

#### Format:

#### Description:

The two-byte contents of register pairs DE and HL are exchanged.

M CYCLES: 1 T STATES: 4 4 MHz E.T.: 1.00

Condition Bits Affected: None

## Example:

If the content of register pair DE is the number 2822H, and the content of the register pair HL is number 499AH, after the instruction

EX DE, HL

the content of register pair DE will be 499AH and the content of register pair HL will be 2822H.

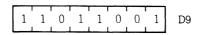

**Operation:** (BC) $\leftrightarrow$ (BC'), (DE) $\leftrightarrow$ (DE'), (HL) $\leftrightarrow$ (HL')

Format:

#### Opcode

EXX

## Description:

Each two-byte value in register pairs BC, DE, and HL is exchanged with the two-byte value in BC', DE', and HL', respectively.

M CYCLES: 1

T STATES: 4

4 MHz E.T.: 1.00

Condition Bits Affected:

None

#### Example:

If the contents of register pairs BC, DE, and HL are the numbers 445AH, 3DA2H, and 8859H, respectively, and the contents of register pairs BC', DE', and HL' are 0988H, 9300H, and 00E7H, respectively, after the instruction

EXX

the contents of the register pairs will be as follows: BC: 0988H; DE: 9300H; HL: 00E7H; BC': 445AH; DE': 3DA2H; and HL': 8859H.

Operation: CPU Halt

Format:

Opcode

HALT

## Description:

The HALT instruction suspends CPU operation until a subsequent interrupt or reset is received. While in the halt state, the processor will execute NOP's to maintain memory refresh logic.

M CYCLES: 1

T STATES: 4

4 MHz E.T.: 1.00

Condition Bits Affected:

None

# IM 0

Operation: Interrupt Mode 0

#### Format:

| Opcode |   |   |   |   |   | Operands |   |    |  |

|--------|---|---|---|---|---|----------|---|----|--|

| IM     |   |   |   |   |   | 0        |   |    |  |

| 1      | 1 | 1 | 0 | 1 | 1 | 0        | 1 | ED |  |

| 0      | 1 | 0 | 0 | 0 | 1 | 1        | 0 | 46 |  |

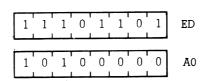

## Description:

The IM 0 instruction sets interrupt mode 0. In this mode the interrupting device can insert any instruction on the data bus and allow the CPU to execute it.

M CYCLES: 2 T STATES: 8(4,4) 4 MHz E.T.: 2.00

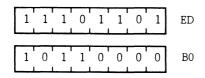

Operation: Interrupt Mode 1

#### Format:

| Opcode |   |   |   |   | Operands |   |   |    |

|--------|---|---|---|---|----------|---|---|----|

| IM     |   |   |   |   | 1        |   |   |    |

| 1      | 1 | 1 | 0 | 1 | 1        | 0 | 1 | ED |

| 0      | 1 | 0 | 1 | 0 | 1        | 1 | 0 | 56 |

## Description:

The IM instruction sets interrupt mode 1. In this mode the processor will respond to an interrupt by executing a restart to location 0038H.

M CYCLES: 2 T STATES: 8(4,4) 4 MHz E.T.: 2.00

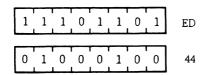

## IM 2

Operation: Interrupt Mode 2.

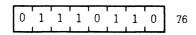

#### Format:

## Description:

The IM 2 instruction sets interrupt mode 2. This mode allows an indirect call to any location in memory. With this mode the CPU forms a 16-bit memory address. The upper eight bits are the contents of the Interrupt Vector Register I and the lower eight bits are supplied by the interrupting device.

M CYCLES: 2 T STATES: 8(4,4) 4 MHz E.T.: 2.00

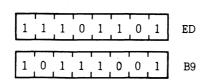

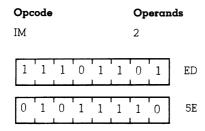

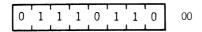

Operation:  $A \leftarrow (n)$

## Format:

## Description:

The operand n is placed on the bottom half (A0 through A7) of the address bus to select the I/O device at one of 256 possible ports. The contents of the Accumulator also appear on the top half (A8 through A15) of the address bus at this time. Then one byte from the selected port is placed on the data bus and written into the Accumulator (register A) in the CPU.

M CYCLES: 3 T STATES: 11(4,3,4) 4 MHz E.T.: 2.75

Condition Bits Affected: None

#### Example:

If the contents of the Accumulator are 23H and the byte 7BH is available at the peripheral device mapped to I/O port address 01H, then after the execution of

IN A (01H)

the Accumulator will contain 7BH.

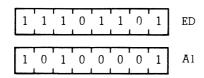

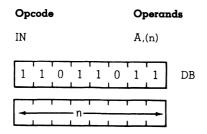

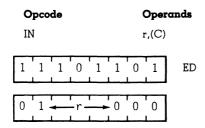

# IN r(C)

Operation:  $r \leftarrow (C)$

#### Format:

### Description:

The contents of regsiter C are placed on the bottom half (A0 through A7) of the address bus to select the I/O device at one of 256 possible ports. The contents of Register B are placed on the top half (A8 through A15) of the address bus at this time. Then one byte from the selected port is placed on the data bus and written into register r in the CPU. Register r identifies any of the CPU registers shown in the following table, which also shows the corresponding 3-bit r field for each. The flags will be affected, checking the input data.

| Register | r   |

|----------|-----|

| В        | 000 |

| С        | 001 |

| D        | 010 |

| E        | 011 |

| Н        | 100 |

| L        | 101 |

| A        | 111 |

M CYCLES: 3 T STA

T STATES: (12(4,4,4)

4 MHz E.T.: 3.00

#### Condition Bits Affected:

S: Set if input data is negative;

reser otherwise

Z: Set if input data is zero;

reset otherwise

H: Reset

P/V: Set if parity is even;

reset otherwise

N: Reset

C: Not affected

#### Example:

If the contents of register C are 07H, the contents of register B are 10H, and the byte 7BH is available at the peripheral device mapped to I/O port address 07H, then after the execution of

IN

$$D_{i}(C)$$

The register D will contain 7BH.

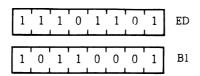

# INC (HL)

Operation:  $(HL)\leftarrow (HL)+1$

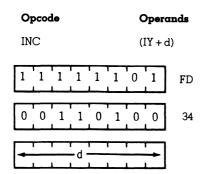

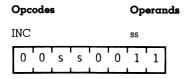

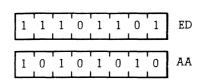

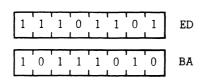

#### Format:

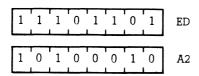

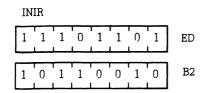

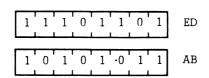

| Opcode |   |   |   |   |   | 0  | perc | ınds |